Pad Cell: Difference between revisions

| Line 34: | Line 34: | ||

[[File:Rail-based ESD Protection.png|none|thumb|Concept of rail-based ESD Protection. ESD current is redirected to the VDD power rail and then shunted to GND by a power clamp.]] | [[File:Rail-based ESD Protection.png|none|thumb|Concept of rail-based ESD Protection. ESD current is redirected to the VDD power rail and then shunted to GND by a power clamp.]] | ||

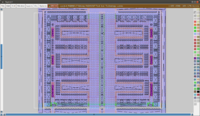

An example layout found in one of the opened up PDKs available can be seen below | An example layout found in one of the opened up PDKs available can be seen below | ||

[[File:ESD layout.png|none|thumb|200x200px|Example ESD layout done in Magic]] | [[File:ESD layout.png|none|thumb|200x200px|Example ESD layout done in Magic]]Consult the following literature for more information: http://www-tcad.stanford.edu/tcad/pubs/theses/chun.pdf | ||

== Bonding pad == | == Bonding pad == | ||

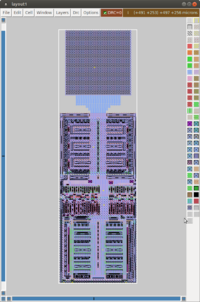

[[File:Bonding Pad.png|none|thumb|200x200px|Example bonding pad done in Magic]] | [[File:Bonding Pad.png|none|thumb|200x200px|Example bonding pad done in Magic]] | ||

Revision as of 12:25, 2 December 2024

A typical pad cell consists of driver logic, ESD protection and a bonding pad, which essentially just is a "large" metal square, big enough to fit a bonding ball needed to attach the bonding wire or solder it to a PCB (flip chip bonding) or onto another carrier substrate chip (chiplet assembly)

Driver Logic

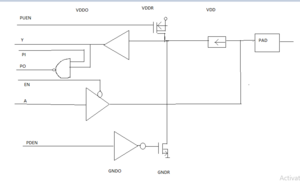

This part of the pad cell is purely combinatorial, and controls based on its pins on the logic side where it's interfacing to the internal logic, what modes should be configured.

For instance, whether the output is enabled, in which case it would either drive current through its driver circuit or pull down to ground in case pull down mode is being set from the internal logic.

It can also be configured for high impedance input, in case OE is disabled.

An example block diagram of a simple IO buffer pad cell can be seen below

Various additional functions can be implemented, like for instance impedance and termination resistor calibration in case it's part of a DRAM or PCIe PHY.

In short, the driver logic configures the actual physical properties of the pad depending on what the internal logic tells it to do:

- Set transistors to either drive from the VCC rail to ground or switch towards ground

- Setting whether the driver should be active at all (Output Enable)

- Provide a state engine or other means for configuring the termination resistance to ground.

Driver circuit

Internally, transistors of a logic circuit only can drive a few micro amperes of current and are unable to survive driving a load like an LED.

In order to make a chip do something useful driver circuits need to be implemented which can provide the power needed for actually driving loads like making an LED blink or driving a small DC motor.

This is being done in the driver circuit through Fingered Transistors which turn the low power logic states at its inputs into a state which is useful to the outside world.

ESD protection

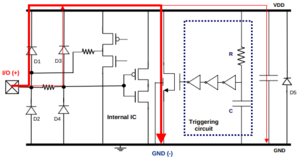

The figure below shows an example of the rail-based protection in which the primary dual diodes (D1 and D2), the secondary dual diodes (D3 and D4), the NMOSFET power supply clamp are employed.

The power clamp provides a current path from the power supply pad to the ground pad during various ESD events.

It's the simplest form of the RC-triggered power supply clamp, where the RC network and the inverter chain are designed such that the NMOSFET (M1) remains off during normal operation and turns on during an ESD event. This NMOSFET should be wide enough to handle the ESD current when it is on during an ESD event.

An example layout found in one of the opened up PDKs available can be seen below

Consult the following literature for more information: http://www-tcad.stanford.edu/tcad/pubs/theses/chun.pdf

Bonding pad