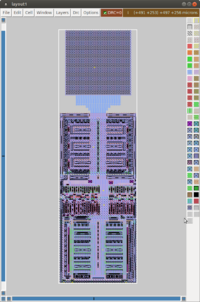

Pad Cell Generator

The LibreSilicon Pad Cell Generator is an extension of the Standard Logic Cell Library generator, which besides the driver logic also dynamically generates the mixed signal parts needed for over current and static discharge protection and providing the currents needed for doing useful things with an actual physical chip, like driving an LED or a small motor.

Note: We are still waiting for the NLNet grant, so there isn't any code to speak of yet for this tool, but the general use of the tool will be pretty much the same as for generating the standard logic cell lib and the Danube River test structures for characterizing your target process.

Existing Groundwork

The generator is based on the work of several folks who started developing puzzle pieces for it before Google ran out of funding internally and the project had to go on hiatus

Here's some works our generator will be based on:

- Gowthami Nalla did some work with the logic circuit and the driver but it's specific to XFAB only; https://github.com/gowthaminalla/bidirectional-buffer/

- Very rudimentary development has been done on the ESD front: https://github.com/AishikAnalogCKTdesign/ESD

- Philip's pad frame generator (Perl): https://www2.futureware.at/~philipp/vsd2018/

- Philip's very basic Perl based pad cell generator (https://pdk.libresilicon.com/PadCellGenerator.zip)

- Perl based

- Not portable

- Needs smarter ESD protection

- Needs smarter IO config

- Doesn't have termination resistor configuration (needed for DDR3/DDR4 PHYs)

Configuration

The Pad Cell Generator has the task of generating a Pad Cell for generating a pad frame for taping out a circuit with any given set of design rules for any given process.

Just as with the Standard Cell Generator, you need to provide the Pad Cell Generator the appropriate configuration telling it about all the design constraints and mixed signal characteristics of the process you are targetting.

Please look at our reference technology folders like the design rule constraints and parameters, for which we introduced a somewhat standardized format with the advent of our Danube River test wafer generator.

https://github.com/thesourcerer8/StdCellLib/tree/master/Tech.GF180MCU

How to use (WIP)

First clone the repository

git clone https://gitlab.libresilicon.com/leviathan/PadCellGenerator.git cd PadCellGenerator

Then you fetch the Dockerimage with all the LibreSilicon tools preinstalled, just as with DanubeRiver and the Standard Logic Cell generator library:

docker pull leviathanch/libresilicon-tools:latest

Then you've got to start the Docker container and build the pad cells for your specific process

xhost +local:docker docker run -e DISPLAY=$DISPLAY -v /tmp/.X11-unix:/tmp/.X11-unix -v `pwd`:/work -it leviathanch/libresilicon-tools

After that there's some make commands telling my Python scripts, which I haven't pushed yet, what to do, as soon as they can actually do it... when depends on NLNet.

For now it's just Perl scripts and some loose Magic files